# 带输出关断的20V, 14A全集成同步升压转换器

## ■ 特点

·输入电压范围V<sub>PIN</sub>: 2.7V-20V

·输出电压范围VOUT: 4.5V-20V

·可编程峰值电流: 14A

· 高转换效率:

95% ( $V_{PIN} = 7.2V$ ,  $V_{OUT} = 16V$ ,  $I_{OUT} = 3A$ )

94% ( $V_{PIN} = 12V, V_{OUT}=18V, I_{OUT}=4A$ )

90% ( $V_{PIN} = 3.3, V_{OUT} = 9V, I_{OUT} = 3A$ )

· 轻载条件下两种调制方式: 脉频调制 (PFM) 和 强制脉宽调试 (PWM)

· 集成输出关断的栅极驱动

·低关断功耗,关断电流1uA

·可调节的开关频率: 200k-1.4M

· 可编程软启动

·输出过压 (22V)、逐周期过流、热关断等保护

· DFN20, 4.5mm\*3.5mm 无铅超薄封装

## ■ 应用

· 无线音箱

· 便携式音箱

· 快充移动电源

· 电子烟

· USB TYPE-C 电源传输

• 拉杆音箱

· 平板电脑, 笔记本电脑

·POS机终端

# ■ 概述

HT7178是一款高功率、全集成升压转换器,带有负载关断功能的栅极驱动,集成16mΩ功率开关管和16mΩ同步整流管,为便携式系统提供高效的小尺寸解决方案。

HT7178具有2.7V至20V宽输入电压范围,可为采用单节或两节锂电池,或12V铅酸电池的应用提供支持。该器件具备14A开关电流能力,并且能够提供高达20V的输出电压。

HT7178采用自适应恒定关断时间峰值电流控制拓扑结构来调节输出电压。在中等到重负载条件下,HT7178 工作在PWM 模式。在轻负载条件下,该器件可通过MODE引脚选择下列两种工作模式之一。一种是可提高效率的PFM模式;另一种是可避免因开关频率较低而引发应用问题的强制PWM模式。PWM模式下,HT7178的开关频率可通过外部电阻调节,支持200kHz至1.4MHz的范围。

HT7178还支持可编程的软启动,以及可调节的 开关峰值电流限制。另外,HT7178集成了输出关断功 能的栅极驱动,在SD状态,可完全断开输入电源。

此外,该器件还提供有22V输出过压保护、逐周期过流保护和热关断保护。

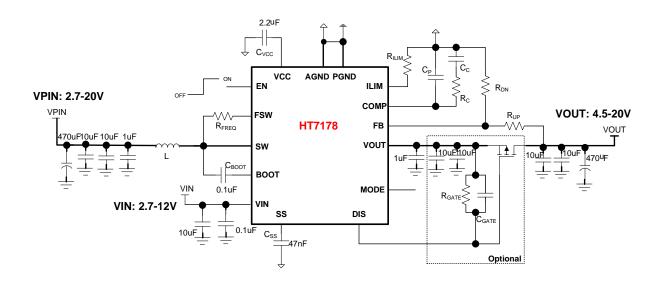

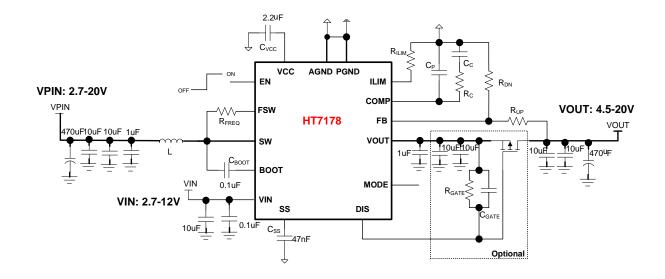

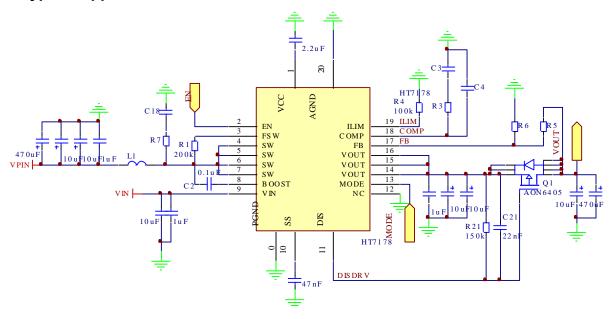

# ■ 典型应用图

# 20V,14A Fully-Integrated Synchronous Boost Converter with Load Disconnect Control

#### **■** FEATURES

- Input voltage range V<sub>PIN</sub>: 2.7V to 20V

- Output voltage range Vou⊤: 4.5V to 20V

- Programmable switch peak current limit: up to 14A

- High Efficiency

95% (V<sub>PIN</sub> = 7.2V, V<sub>OUT</sub>=16V, I<sub>OUT</sub> =3A)

$94\% (V_{PIN} = 12V, V_{OUT} = 18V, I_{OUT} = 4A)$

90% ( $V_{PIN} = 3.3$ ,  $V_{OUT} = 9V$ ,  $I_{OUT} = 3A$ )

- 2 modulation mode available: PFM or PWM mode at light load

- Integrated gate driver for load disconnect and output short protection

- 1.0µA current consumption during shutdown

- Adjustable switching frequency: 200k to 1.4MHz

- Programmable soft start

- Output overvoltage protection (at 22V), cycle-bycycle overcurrent protection, thermal shutdown protection

- Pb-free Packages, DFN20, 4.5mm\*3.5mm

#### APPLICATIONS

- Wireless/ Speakers

Portable Speakers

- Quick Charge Power Bank

E-Cigarette

- Power Interface (USB Type-C, Thunderbolt)

- POS Terminal

Tablet PC/Note Book

#### **■ DESCRIPTION**

The HT7178 is a high-power density, fully integrated synchronous boost converter with a  $16m\Omega$  power switch and a  $16m\Omega$  rectifier switch to provide a high efficiency and small size solution in portable systems. The HT7178 has wide input voltage range from 2.7 V to 20 V to support applications with single cell, two cell Lithium batteries and 12V lead-acid batteries. The device has 14A switch current capability and can provide an output voltage up to 20V.

The HT7178 uses adaptive constant off-time peak current control topology to regulate the output voltage. In moderate to heavy load condition, it works in the PWM mode. In light load condition, the device has two operation modes selected by the MODE pin. One is PFM mode to improve the efficiency and another one is the forced PWM mode to avoid application problems caused by low switching frequency. The switching frequency in the PWM mode is adjustable ranging from 200kHz to 1.4MHz by an external resistor.

HT7178 could isolate the output from input side when shut down by a gate drive output disconnecting external FET, so that the load current consumption could be limited.

The HT7178 also implements a programmable softstart function and an adjustable switching peak current limit function. In addition, the device provides 22V output overvoltage protection, cycleby-cycle overcurrent protection, and thermal shutdown protection.

# **■ TYPICAL APPLICATION**

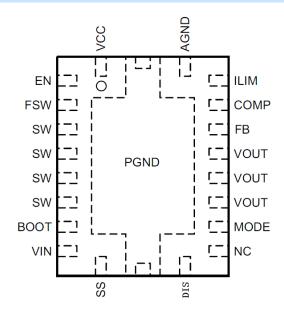

# **■ TERMINAL CONFIGURATION**

# **■ TERMINAL FUNCTION**

| Terminal<br>No. | NAME | I/O*1 | Description                                                                                                                                                                                            |

|-----------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | VCC  | 0     | Output of the internal regulator. A ceramic capacitor of 2.2uF is required between this pin and ground.                                                                                                |

| 2               | EN   | l     | Enable logic input. Logic high level enables the device. Logic low level disables the device and turns it into shutdown mode.                                                                          |

| 3               | FSW  | I     | The switching frequency is programmed by a resister between this pin and the SW pin.                                                                                                                   |

| 4/5/6/7         | SW   | PWR   | The switching node pin of the converter.                                                                                                                                                               |

| 8               | ВООТ | 0     | Power supply for high-side MOSTFET gate driver. A ceramic capacitor of 0.1µF must be connected between this pin and the SW pin.                                                                        |

| 9               | VIN  | I     | IC power supply input.                                                                                                                                                                                 |

| 10              | SS   | 0     | Soft-start programming pin. An external capacitor connected to ground sets the ramp rate of the internal error amplifier's reference voltage during soft-start                                         |

| 11              | DIS  | 0     | A gate drive output for the external disconnect FET. Connect the DISDRV pin to the gate of the external FET. Leave it floating if not using the load disconnect function.                              |

| 12              | NC   | -     | No connection inside the device. Connect these two pins to ground plane on the PCB for good thermal dissipation.                                                                                       |

| 13              | MODE | I     | Operation mode selection pin for the device in light load condition. When this pin is connected to ground, the device works in PWM mode. When this pin is left floating, the device works in PFM mode. |

| 14/15/16        | VOUT | PWR   | Boost converter output.                                                                                                                                                                                |

| 17              | FB   | I     | Voltage feedback.                                                                                                                                                                                      |

| 18              | COMP | 0     | Output of the internal error amplifier, the loop compensation network should be connected between this pin and the AGND pin.                                                                           |

| 19              | ILIM | I     | Adjustable switch peak current limit. An external resister should be connected between this pin and the AGND pin.                                                                                      |

| 20              | AGND | -     | Signal ground of the IC.                                                                                                                                                                               |

| 0               | PGND | PWR   | Power ground of the IC.                                                                                                                                                                                |

<sup>\*1</sup> I: input O: output PWR: power

# ■ ORDERING INFORMATION

| Part Number | Package Type | Marking            | Operating<br>Temperature Range | MOQ/Shipping<br>Package |

|-------------|--------------|--------------------|--------------------------------|-------------------------|

| HT7178      | DFN20        | HT7178<br>UVWXYZ*2 | -40°C∼85°C                     | Reel                    |

<sup>\*2:</sup> UVWXYZ is production track code.

#### **■ ELECTRICAL CHARACTERISTIC**

# Absolute Maximum Ratings\*3

|                                      | Symbol                   | MIN              | MAX  | UNIT |            |

|--------------------------------------|--------------------------|------------------|------|------|------------|

|                                      | BOOT                     |                  | -0.3 | SW+7 | V          |

|                                      | SW, FSW, Vout, DIS, VPIN |                  | -0.3 | 22.5 |            |

| Voltage range                        | Vin                      | /                | -0.3 | 14   |            |

|                                      | EN, VCC, SS, COMP, MODE  |                  | -0.3 | 7    |            |

|                                      | ILIM, FB                 |                  | -0.3 | 3.6  |            |

| Operating temperature range          |                          | TA               | -40  | 85   | $^{\circ}$ |

| Operating junction temperature range |                          | TJ               | -40  | 150  | $^{\circ}$ |

| Storage temperature range            |                          | T <sub>STG</sub> | -50  | 150  | $^{\circ}$ |

<sup>\*3:</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

#### Recommended Operating Conditions

| PARAMETER                           | Symbol          | CONDITION | MIN  | TYP | MAX  | UNIT                 |

|-------------------------------------|-----------------|-----------|------|-----|------|----------------------|

| Input power voltage range           | VPIN            |           | 2.7  |     | 20   | V                    |

| IC power supply voltage range       | V <sub>IN</sub> |           | 2.7  |     | 12   | V                    |

| Output voltage range                | Vouт            |           | 4.5  |     | 20   | V                    |

| Inductance, effective value         | L               |           | 0.47 | 2.2 | 10   | μH                   |

| Input capacitance, effective value  | Cı              |           | 10   |     | 0.4  | μF                   |

| Output capacitance, effective value | Со              |           | 6.8  | 47  | 1000 | μF                   |

| Operating temperature               | Ta              |           | -40  | 25  | 85   | $^{\circ}\mathbb{C}$ |

| Operating junction temperature      | TJ              |           | -40  |     | 125  | $^{\circ}\mathbb{C}$ |

# ● Electrical Characteristics\*4

Condition: Ta = 25 $^{\circ}$ C, V<sub>PIN</sub> = 2.7V-20V, V<sub>OUT</sub>=4.5-20V, unless otherwise specified.

| PARAMETER                                               | Symbol                | CONDITION                                                                | MIN   | TYP   | MAX   | UNIT |

|---------------------------------------------------------|-----------------------|--------------------------------------------------------------------------|-------|-------|-------|------|

| Power Supply                                            |                       |                                                                          |       |       |       |      |

| Input power voltage range                               | V <sub>PIN</sub>      |                                                                          | 2.7   |       | 20    | V    |

| IC power supply voltage range                           | Vin                   |                                                                          | 2.7   |       | 12    | V    |

| Under-voltage lockout                                   | V                     | VIN rising                                                               |       |       | 2.7   | V    |

| (UVLO) threshold                                        | V <sub>IN_UVLO</sub>  | VIN falling                                                              |       |       | 2.5   | V    |

| VIN UVLO hysteresis                                     | V <sub>IN_HYS</sub>   |                                                                          |       | 200   |       | mV   |

| VCC UVLO threshold                                      | $V_{\text{CC\_UVLO}}$ |                                                                          |       | 2.1   |       | V    |

| Operating                                               |                       | $V_{IN} = V_{PIN} = 3.3V, V_{OUT} = 7.5V$                                |       | 600   |       |      |

| quiescent<br>current V <sub>PIN</sub> + V <sub>IN</sub> | ΙQ                    | $V_{IN} = V_{PIN} = 7.2V, V_{OUT} = 12V$                                 |       | 390   |       | uA   |

| from                                                    |                       | $V_{IN} = V_{PIN} = 12V$ , $V_{OUT} = 18V$                               |       | 460   |       |      |

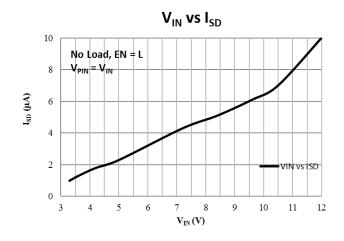

| Shutdown current into                                   | los                   | IC disabled, V <sub>IN</sub> =V <sub>PIN</sub> = 3.6 V                   |       | 1     |       | uA   |

| $V_{PIN} + V_{IN}$                                      | Isp                   | IC disabled, V <sub>IN</sub> =V <sub>PIN</sub> = 7.4 V                   |       | 4     |       |      |

| VCC regulation                                          | Vcc                   |                                                                          |       | 5.2   |       | V    |

| EN and Mode Input                                       |                       |                                                                          |       |       |       |      |

| EN high threshold voltage                               | $V_{ENH}$             |                                                                          | 1.5   |       |       | V    |

| EN low threshold voltage                                | V <sub>ENL</sub>      |                                                                          |       |       | 0.4   | V    |

| EN internal pull-down resistance                        | Ren                   |                                                                          |       | 800   |       | kΩ   |

| MODE high threshold voltage                             | V <sub>MODEH</sub>    |                                                                          | 4     |       |       | V    |

| MODE low threshold voltage                              | VMODEL                |                                                                          |       |       | 1.5   | V    |

| MODE internal pull-up resistance                        | R <sub>MODE</sub>     |                                                                          |       | 800   |       | kΩ   |

| OUTPUT                                                  |                       |                                                                          |       |       |       |      |

| Output voltage range                                    | V <sub>out</sub>      | Freq = 500 kHz                                                           | 4.5   |       | 20    | V    |

| Output overvoltage                                      |                       | 1 10q = 300 KHZ                                                          |       |       |       |      |

| protection  Reference voltage at                        | Vovp                  |                                                                          | 21.5  | 22    | 22.5  | V    |

| the FB pin                                              | VREF                  |                                                                          | 1.186 | 1.204 | 1.222 | V    |

| Soft-start charging current                             | I <sub>SS</sub>       |                                                                          |       | 5     |       | uA   |

| ERROR AMPLIFIER                                         |                       |                                                                          |       |       |       |      |

| COMP pin sink current                                   | I <sub>SINK</sub>     | $V_{FB} = V_{REF} + 200 \text{ mV}, V_{COMP} = 1.5 \text{ V}$            |       | 20    |       | uA   |

| COMP pin source current                                 | Isource               | V <sub>FB</sub> = V <sub>REF</sub> -200 mV, V <sub>COMP</sub> = 1.5 V    |       | 20    |       | uA   |

| High clamp voltage at the COMP pin                      | V <sub>CC_LPH</sub>   | $V_{FB} = 1 \text{ V}, \text{ R}_{ILIM} = 100 \text{ k}\Omega$           |       | 2.3   |       | V    |

| Low clamp voltage at the COMP pin                       | Vcc_lpl               | $V_{FB} = 1.5 \text{ V}, \text{ R}_{\text{ILIM}} = 100 \text{ k}\Omega,$ |       | 1.4   |       | V    |

| Error amplifier transconductance                        | GEA                   | V <sub>COMP</sub> = 1.5 V                                                |       | 190   |       | uA/V |

| POWER SWITCH                                            |                       |                                                                          |       |       |       |      |

| MOSFET on-                                              | R <sub>DS(on)</sub>   | High-side MOSFET                                                         |       | 16    |       | mΩ   |

| resistance                                              | 1 (100(011)           | Low-side MOSFET                                                          |       | 16    |       | mΩ   |

| CURRENT LIMIT                                           |                       |                                                                          |       |       |       |      |

| Peak switch current                                     | li na                 | $R_{ILIM} = 100 \text{ k}\Omega,$                                        | 11    | 12    | 13    |      |

| limit                                                   | Ішм                   | $R_{ILIM} = 82 \text{ k}\Omega,$                                         | 13    | 14    | 15    | A    |

| Reference voltage at the ILIM pin                       | VILIM                 |                                                                          |       | 1.204 |       | V    |

| SWITCHING FREQUEN                                       | ICY                   |                                                                          |       |       |       |      |

| Switching frequency fsw             |                     | $R_{FREQ}$ = 220 k $\Omega$ , $V_{PIN}$ = 3.6V, $V_{OUT}$ = 12V |  | 600 |     | kHz          |

|-------------------------------------|---------------------|-----------------------------------------------------------------|--|-----|-----|--------------|

| Minimum on-time ton_min             |                     | $R_{FREQ}$ = 220 k $\Omega$ , $V_{PIN}$ = 3.6V, $V_{OUT}$ = 12V |  | 90  | 180 | ns           |

| GATE DRIVER FOR LOAD DISCONNECT     |                     |                                                                 |  |     |     |              |

| Driver current for the external FET |                     |                                                                 |  | 55  |     | uA           |

| THERMAL SHUTDOWN                    |                     |                                                                 |  |     |     |              |

| Thermal shutdowr threshold          | T <sub>SD</sub>     |                                                                 |  | 150 |     | $^{\circ}$ C |

| Thermal shutdowr hysteresis         | T <sub>SD_HYS</sub> |                                                                 |  | 20  |     | $^{\circ}$ C |

<sup>\*4:</sup> Depending on parts and pattern layout, characteristics may be changed.

# • Voltage Setting Reference for HT7178

| Input<br>Power       | Referred Max<br>Input Current<br>(RMS Value) | Input<br>Voltage     | Output<br>Voltage | Referred Max<br>Output Current<br>(RMS Value) | Output<br>Power         | Efficiency | Pull-up<br>resistor<br>from FB | Pull-down<br>resistor<br>from FB |

|----------------------|----------------------------------------------|----------------------|-------------------|-----------------------------------------------|-------------------------|------------|--------------------------------|----------------------------------|

| P <sub>PIN</sub> (W) | I <sub>PIN</sub> (A)                         | V <sub>PIN</sub> (V) | Vout(V)           | <b>I</b> оит <b>(A)</b>                       | <b>Р</b> оит <b>(W)</b> | η(%)       | $R_{UP}(\Omega)$               | $R_{DN}(\Omega)$                 |

| 33.30                | 9.0                                          | 3.7                  | 7.3               | 4.0                                           | 29.20                   | 87.7%      | 510k                           | 100k                             |

| 35.15                | 9.5                                          | 3.7                  | 9.4               | 3.3                                           | 31.02                   | 88.3%      | 510k                           | 75k                              |

| 34.78                | 9.4                                          | 3.7                  | 12.2              | 2.5                                           | 30.50                   | 87.7%      | 510k                           | 56k                              |

| 68.08                | 9.2                                          | 7.4                  | 12.2              | 5.2                                           | 63.44                   | 93.2%      | 510k                           | 56k                              |

| 67.86                | 9.2                                          | 7.4                  | 15.5              | 4.0                                           | 62.00                   | 91.4%      | 510k                           | 43k                              |

| 74.00                | 10.0                                         | 7.4                  | 18.3              | 3.6                                           | 65.88                   | 89.0%      | 510k                           | 36k                              |

| 117.48               | 9.8                                          | 12                   | 18.3              | 6.0                                           | 109.80                  | 93.5%      | 510k                           | 36k                              |

| 124.80               | 10.4                                         | 12                   | 19.5              | 6.0                                           | 117.00                  | 93.8%      | 510k                           | 33k                              |

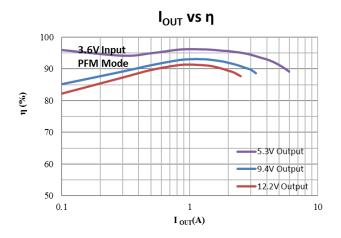

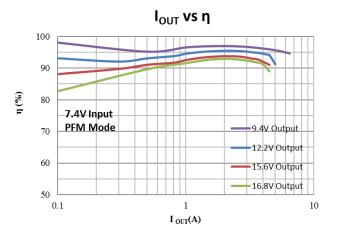

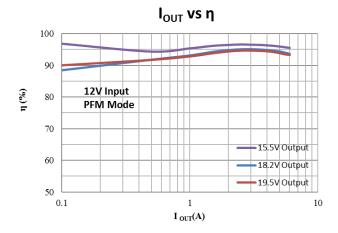

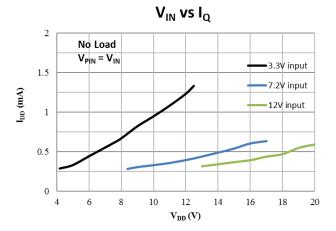

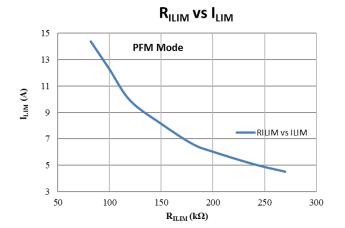

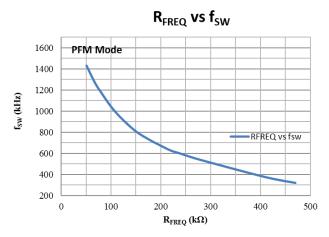

## **■ TYPICAL OPERATING CHARACTERISTICS**

$Condition: L = 1.5 uH, \ R_{ILIM} = 82 k, \ \ R_{FREQ} = 200 k, \ Output \ Capacitor = 1 uF//10 uF//10 uF//220 uF, \ PFM \ mode, \ otherwise \ specified.$

#### APPLICATION INFORMATION

# 1. Typical Application

Do make sure that the voltage peak of pin  $V_{IN}$  should be lower than 12V. If the input power voltage is higher than 12V ( $V_{PIN} > 12V$ ), use a 3.3V or 5V logic power supply to connect  $V_{IN}$  or use a lager resistor connecting between  $V_{PIN}$  and  $V_{IN}$ .

# 2. Feature Description

# 2.1. Functional Modes (Mode pin)

#### Operation

The synchronous boost converter HT7178 operates at a quasi-constant frequency pulse width modulation (PWM) in moderate to heavy load condition. Based on the V<sub>PIN</sub> to V<sub>OUT</sub> ratio, a circuit predicts the required off-time of the switching cycle. At the beginning of each switching cycle, the low-side N-MOSFET switch is turned on, and the inductor current ramps up to a peak current that is determined by the output of the internal error amplifier. After the peak current is reached, the current comparator trips, and it turns off the low-side N-MOSFET switch and the inductor current goes through the body diode of the high-side N-MOSFET in a dead-time duration. After the dead-time duration, the high-side N-MOSFET switch is turned on. Because the output voltage is higher than the input voltage, the inductor current decreases. The high-side switch is not turned off until the fixed off-time is reached. After a short dead-time duration, the low-side switch turns on again and the switching cycle is repeated.

In light load condition, the HT7178 implements two operation modes, PFM mode and forced PWM mode, to meet different application requirements. The operation mode is set by the status of the MODE pin. When the MODE pin is connected to ground, the device works in the forced PWM mode. When the MODE pin is left floating, the device works in the PFM mode, which is the recommended mode.

#### **PWM Mode**

In the forced PWM mode, the HT7178 keeps the switching frequency unchanged in light load condition. When the load current decreases, the output of the internal error amplifier decreases as well to keep the inductor peak current down, delivering less power from input to output. When the output current further reduces, the current through the inductor will decrease to zero during the off-time. The high-side N-MOSFET is not turned off even if the current through the MOSFET is zero. Thus, the inductor current changes its direction after it runs to zero. The power flow is from output side to input side. The efficiency will be low in this mode. But with the fixed switching frequency, there is no audible noise and other problems which might be caused by low switching frequency in light load condition.

#### **PFM Mode**

The HT7178 improves the efficiency at light load with the PFM mode. When the converter operates in light load condition, the output of the internal error amplifier decreases to make the inductor peak current down, delivering less power to the load. When the output current further reduces, the current through the inductor will decrease to zero during the off-time. Once the current through the high side N-MOSFET is zero, the high-side MOSFET is turned off until the beginning of the next switching cycle. When the output of the error amplifier continuously goes down and reaches a threshold with respect to the peak current of ILIM / 12, the output of the error amplifier is clamped at this value and does not decrease any more. If the load current is smaller than what the HT7178 delivers, the output voltage increases above the nominal setting output voltage. The HT7178 extends its off time of the switching period to deliver less energy to the output and regulate the output voltage to 0.7% higher than the nominal setting voltage. With the PFM operation mode, the HT7178 keeps the efficiency above 80% even when the load current decreases to 1 mA. In addition, the output voltage ripple is much smaller at light load due to low peak current.

#### 2.2. Enable and Startup (EN and SS pin)

The HT7178 has an adjustable soft start function to prevent high inrush current during start-up. To minimize the inrush current during start-up, an external capacitor, connected to the SS pin and charged with a constant current, is used to slowly ramp up the internal positive input of the error amplifier. The larger the capacitance at the SS pin, the slower the ramp of the output voltage and the longer the soft-start time. A 47-nF capacitor is usually sufficient for most applications.

When the EN pin is pulled into logic low (below 0.4V), the HT7178 goes into the shutdown mode and stops switching. Only when EN pin is pulled into logic high (above 1.5V), the HT7178 works.

## 2.3. Adjustable Switching Frequency (FSW pin)

This device features a wide adjustable switching frequency ranging from 200 kHz to 1.4MHz. The switching frequency is set by a resistor ( $R_{FREQ}$ ) connected between the FSW pin and the SW pin of the HT7178.  $R_{FREQ}$  must always be connected from the FSW pin to SW pin for proper operation.  $R_{FREQ}$  can be calculated by:

$$R_{FREQ} = \frac{4 \times (\frac{1}{f_{SW}} - t_{DELAY} \times \frac{V_{OUT}}{V_{PIN}})}{C_{FREQ}}$$

where

- Reference is the resistance connected between the FSW pin and the SW pin.

- C<sub>FREQ</sub> = 23pF.

- f<sub>SW</sub> is the desired switching frequency.

- t<sub>DELAY</sub> = 89 ns.

- V<sub>PIN</sub> is the input voltage.

- V<sub>OUT</sub> is the output voltage.

NOTE: A resistor value of 180-300k is recommended for R<sub>FREQ</sub> to get a f<sub>SW</sub> of around 450-700kHz.

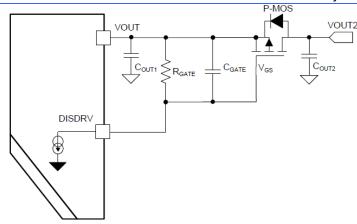

#### 2.4. Load Disconnect Gate Driver (DIS pin)

The HT7178 provides a DIS pin to drive the external FET at the output side, which completely disconnects the output from the input end during shutdown or output short happens. During the device's start-up phase, the disconnect FET is controlled by the gate driver voltage of the external disconnect FET, there is an internal 55µA (typical) sink current. The load disconnect FET connection is shown as Figure 1. Do make sure that Cout2 should be no larger than 10 x Cout1 to avoid the inrush current when turning on the disconnect FET.

Figure 1 Load Disconnect FET Connection

The FET parameter should be considered as follows:

- The drain-to-source voltage rating V<sub>DS</sub> should be higher than the output max. voltage V<sub>OUT</sub>.

- The drain-to-source RMS current rating  $I_{DS}(RMS)$  should be higher than the maximum output current.

The driver voltage and turn on / off timing can be set via the resistor R<sub>GATE</sub> and capacitor C<sub>GATE</sub> connecting between with the DIS pin and the source of the external FET. 150K and 22nF can be used in most cases.

To set the C<sub>GATE</sub>, the following equation can be used:

$$C_{GATE} \approx C_{GS\_PFET} = \frac{T_{ON\_PFET} \times I_{DIS\_PFET}}{V_{TH\_PFET}}$$

where

- C<sub>GS\_PFET</sub> is the total gate capacitance of connected between gate and source external FET. (including the self-gate-source capacitance of the FET). The maximum capacitance C<sub>GS\_PFET</sub> should be < 100nF.

- Ton\_PFET is the turn on time of external FET. The max Ton\_PFET should not exceed 3ms

- IDIS\_PFET is the discharge current inside of HT7178, it is 55µA typically.

- V<sub>TH\_PFET</sub> is the gate threshold of external FET.

To set the RGATE, the following equation can be used:

$$R_{GATE} = \frac{V_{GATE}}{I_{DIS\_PFET}}$$

While DIS is not used, it can be connected to GND so that a more integral GND plane can be achieved to decrease the loop of output peak current.

#### 2.5. Adjustable Peak Current Limit (ILIM pin)

To avoid an accidental large peak current, an internal cycle-by-cycle current limit is adopted. The low-side switch is turned off immediately as soon as the switch current touches the limit. The peak switch current limit can be set by a resistor (R<sub>ILIM</sub>) at the ILIM pin to ground. The relationship between the current limit and the resistance is as follows:

$$I_{LIM} = \frac{1200000}{R_{ILIM}}$$

# 2.6. Output Voltage Setting (FB pin)

The output voltage is set by an external resistor divider (R<sub>UP</sub>, R<sub>DN</sub> in the Typical Application Circuit). To get the output voltage V<sub>OUT</sub>, the Value of R<sub>UP</sub> and R<sub>DN</sub> can be calculated as:

$$V_{OUT} = V_{REF} \times (1 + \frac{R_{UP}}{R_{DN}})$$

Where  $V_{REF} = 1.204V$ .

Some typical output voltages can be set as the following parameters.

| V <sub>OUT</sub> (V) | $R_{UP}(\Omega)$ | $R_{DN}(\Omega)$ |

|----------------------|------------------|------------------|

| 9.4                  | 510k             | 75k              |

| 12.2                 | 510k             | 56k              |

| 15.5                 | 510k             | 43k              |

| 18.3                 | 510k             | 36k              |

#### 2.7. Inductor Selection (SW pin)

Because the selection of the inductor affects the power supply's steady state operation, transient behavior, loop stability, and boost converter efficiency, the inductor is the most important component in switching power regulator design. Three most important specifications to the performance of the inductor are the inductor value, DC resistance, and saturation current.

To be simplified, the inductor value can be set as 2.2uH which can be used in most cases.

The rated current, especially the saturation current should be larger than the peak current during the whole operation. The peak current can be calculated as follows.

$$I_{Lpeak} = I_{DC} + \frac{I_{PP}}{2}$$

$$I_{DC} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta}$$

$$I_{PP} = \frac{1}{L \times (\frac{1}{V_{OUT} - V_{IN}} + \frac{1}{V_{IN}}) \times f_{SW}}$$

Boost converter efficiency is affected significantly by the inductor's DC resistance (DCR), equivalent series resistance (ESR) at the switching frequency, and the core loss. An inductor with lower DCR and ESR would increase the efficiency significantly.

The inductor should be placed as close as possible to the SW pin. For a lower EMI radiation, connecting a resistor and a capacitor in series to the ground would be helpful. 10hm resistor and 10nF capacitor would be recommended in most cases.

#### 2.8. Input Capacitor Selection (VIN, VPIN, VCC pin)

For good input voltage filtering and small voltage ripple (less than 100mV is required), we recommend low-ESR capacitors of 1uF//10uF//10uF//470uF ("//" represents paralleled) be placed as close as possible to the inductor.

The  $V_{IN}$  pin is the power supply for the HT7178, a 1uF paralleled with 10uF ceramic capacitor should be placed as close as possible to the  $V_{IN}$  pin. Notice that the maximum voltage of  $V_{IN}$  should be lower than 12V, so if  $V_{IN}$  is supplied from  $V_{PIN}$ , a resistor of 10R is required between input power supply  $V_{PIN}$  and  $V_{IN}$  pin so that the power supply of HT7178 would be more stable, and if  $V_{PIN}$  is larger than 12V, the value of the resistor should be higher to get a lower voltage of  $V_{IN}$ . An extensive power supply such as the logic power supply connecting to  $V_{IN}$  would be another choice. Be aware of that the current consumption of  $V_{IN}$  is lower than 10mA.

The VCC pin is the output of internal LDO. A ceramic capacitor of 2.2uF is required at the VCC pin to get a stable operation of LDO.

# 2.9. Output Capacitor Selection (Vout pin)

To be simplified, we recommend low-ESR capacitors of 1uF//10uF//10uF//470uF ("//" represents paralleled) be placed as close as possible to VOUT pin for small output voltage ripple.

Capacitors can lose most of their capacitance at rated voltage. Therefore, leave margin on the voltage rating to ensure adequate effective capacitance.

In detail, for the require output voltage ripple, use the following equations to calculate the minimum required effective capacitance Cout

$$V_{ripple\_dis} = \frac{(V_{OUT} - V_{PIN_{MIN}}) \times I_{OUT}}{V_{OUT} \times f_{SW} \times C_{OUT}}$$

$$V_{ripple\_ESR} = I_{Lpeak} \times R_{C\_ESR}$$

#### Where

- V<sub>ripple\_dis</sub> is output voltage ripple caused by charging and discharging of the output capacitor.

- V<sub>ripple\_ESR</sub> is output voltage ripple caused by ESR of the output capacitor.

- VPIN MIN is the minimum input voltage of boost converter...

- V<sub>OUT</sub> is the output voltage..

- lout is the output current.

- · ILpeak is the peak current of the inductor.

- fsw is the converter switching frequency.

- R<sub>C\_ESR</sub> is the ESR of the output capacitors.

#### 2.10. Loop Stability (COMP pin)

The HT7178 requires external compensation, which allows the loop response to be optimized for each application. The COMP pin is the output of the internal error amplifier. An external compensation network comprised of resister R<sub>C</sub>, ceramic capacitors C<sub>C</sub> and C<sub>P</sub> is connected to the COMP pin.

To be simplified,  $R_C$  is  $56k\Omega$ ,  $C_C$  is 3.3nF, and  $C_P$  can be floating. But notice that this setting can only be adopted in most cases. In detail, the compensation network parameters can be calculated as follows.

(1) Set the cross over frequency,  $f_c$

The first step is to set the loop crossover frequency,  $f_{\rm C}$ . The higher crossover frequency, the faster the loop response is. It is generally accepted that the loop gain cross over no higher than the lower of either 1/10 of the switching frequency,  $f_{\rm SW}$ , or 1/5 of the RHPZ frequency,  $f_{\rm RHPZ}$ . It's proper to use a fixed parameter of 10kHz for  $f_{\rm C}$ .

$$f_{RHPZ} = \frac{R_O \times (1 - D)^2}{2\pi \times L}$$

(2) Set the compensation resistor, Rc.

$$R_C = \frac{2\pi \times V_{OUT} \times R_{sense} \times f_C \times C_O}{(1 - D) \times V_{RFF} \times G_{FA}}$$

(3) Set the compensation zero capacitor, Cc

$$C_C = \frac{R_O \times C_O}{2 \times R_C}$$

(4) Set the compensation pole capacitor, CP

$$C_P = \frac{R_{ESR} \times C_O}{R_C}$$

If the C<sub>P</sub> is less than 10pF, it can be left open.

- Ro is the output load resistance.

- D is the switching duty cycle. 1 D = V<sub>PIN</sub> / V<sub>OUT</sub>

- R<sub>sense</sub> is the equivalent internal current sense resistor, which is 0.084  $\Omega$ .

- Co is output capacitor.

- V<sub>REF</sub> is the reference voltage at the FB pin, which is 1.204V.

- GEA is the amplifier's transconductance, which is 190uA/V.

- Resr is the equivalent series resistance of the output capacitor.

#### 2.11. Selecting the Bootstrap Capacitor (BOOT pin)

The bootstrap capacitor ( $C_{BST}$ ) between the BOOT and SW pin supplies the gate current to charge the high-side FET device gate during each cycle's turn-on and supplies charge for the bootstrap capacitor. The recommended value of the bootstrap capacitor is  $0.1\mu F$  to  $1\mu F$ .  $C_{BST}$  should be a good quality, low ESR, ceramic capacitor located at the pins of the device to minimize potentially damaging voltage transients caused by trace inductance. A value of  $0.1\mu F$  can be used in most cases.

#### 2.12. Protection Function

#### **Under-voltage Lockout (UVLO)**

The UVLO circuit prevents the device from malfunctioning at low input voltage and the battery from excessive discharge. The HT7178 has both  $V_{IN}$  UVLO function and VCC UVLO function. It disables the device from switching when the falling voltage at the  $V_{IN}$  pin trips the UVLO threshold  $V_{IN\_UVLO}$ , which is typically 2.4V. The device starts operating when the rising voltage at the VIN pin is 200mV above the  $V_{IN\_UVLO}$ . It also disables the device when the falling voltage at the VCC pin trips the UVLO threshold  $V_{CC\_UVLO}$ , which is typically 2.1V.

# Over-voltage Protection

If the output voltage at the VOUT pin is detected above 22 V (typical value), the HT7178 stops switching immediately until the voltage at the VOUT pin drops the hysteresis value lower than the output overvoltage protection threshold. This function prevents overvoltage on the output and secures the circuits connected to the output from excessive overvoltage.

#### **Thermal Shutdown**

A thermal shutdown is implemented to prevent damages due to excessive heat and power dissipation. Typically, the thermal shutdown happens at a junction temperature of 150°C. When the thermal shutdown is triggered, the device stops switching until the junction temperature falls below typically 130°C, then the device starts switching again.

# 3. Application Notes

#### 3.1. Radiated EMI Reduction

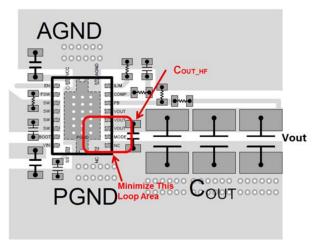

#### (1) Minimize High di/dt Path Loop Area

EMI Starts off from high di/dt loops. The high di/dt critical path locates as the red circle showed in the following figure. The output capacitor should be placed as close to the VOUT pin as possible resulting in minimum area of the high di/dt loop.

The DIS pin (when not used) and NC pin can be connected to PGND ground plane which is good for thermal dissipation, can reduce the impedance of the return path and make the placement of the output capacitors easier.

Figure 2 Critical Path Layout

#### (2) PCB Trace and Ground Plane

High trace inductance leads to poor radiation EMI. The inductance of a PCB trance is a function of its length and width. So, increase the trace width and decrease the trace length will significantly decrease the radiation EMI

Meanwhile, good designed ground planes will help decrease the radiation EMI too:

- Placing a solid ground plane with minimum distance to the critical trace;

- Wider and bigger ground plane result in smaller signal trace inductance;

- Thinner insulation thickness between the ground plane and the signal traces also results in smaller inductance;

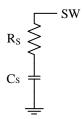

#### (3) RC Snubber

Adding an RC snubber across the SW pin and the power ground can help reduce the radiation EMI levels. The RC snubber should be placed as close as possible to the switching node and the power ground.

Figure 3 Placement of RC Snubber

The aim of the snubber resistor RS is to add sufficient damping to the parasitic resonant circuit. The value of  $R_S$  depends on the desired damping factor and the parasitic inductor  $I_P$  and parasitic capacitor  $C_P$  of the circuit:

$$R_S = \frac{1}{\xi} \times \sqrt{\frac{L_P}{C_P}}$$

Where  $\xi$  is the damping factor, normally can range from 0.5 to 1.

The value of LP and CP can be measured by:

- Measure the original ringing frequency f<sub>RING</sub>;

- Add some small capacitance from switch node to ground. Keep increasing capacitance until the ringing frequency is 50% of the original ringing frequency f<sub>RING</sub>, and the capacitance is C<sub>S</sub>, C<sub>P</sub> = 1/(3C<sub>S</sub>);

$$\bullet \quad L_P = \frac{1}{C_P \times (2\pi \times f_{RING})^2}$$

To be simplified, a resistor of 10hm ( $R_S$ ) and a capacitor of 2.2nF ( $C_S$ ) can be used. However, notice that larger  $C_S$  results in higher power loss.

#### (4) Radiation from Cables

A longer input or output cables result in poor radiation EMI. So, make the length of input cable and output cable very close to the real application.

#### (5) Ferrite Bead

Ferrite Bead is used in series with the power line. Before using a ferrite bead, you need to consider about the specifications of the bead as follows:

The frequency characteristics

Make sure that the resistive impedance of the bead is much higher than the reactive impedance in the noise frequency range.

The rated current

Make sure that the rated current of the bead should be at least 30% higher than the expected maximum current.

The DC resistance

The DC resistance of the ferrite bead should be as low as possible.

#### 3.2. Layout Guidelines

As for all switching power supplies, especially those running at high switching frequency and high currents, layout is an important design step. If layout is not carefully done, the regulator could suffer from instability and noise problems. To maximize efficiency, switch rise and fall times are very fast. To prevent radiation of high frequency noise (for example, EMI), proper layout of the high-frequency switching path is essential. Minimize the length and area of all traces connected to the SW pin, and always use a ground plane under the switching regulator to minimize interplane coupling.

The input capacitor needs to be close to inductor L, the  $V_{IN}$  pin and GND pin in order to reduce the input supply ripple. The output capacitor needs to be close to  $V_{OUT}$  pin and GND pin in order to reduce the output supply ripple.

The layout should also be done with well consideration of the thermal as this is a high-power density device. A thermal pad that improves the thermal capabilities of the package should be soldered to the large ground plate, using thermal vias underneath the thermal pad.

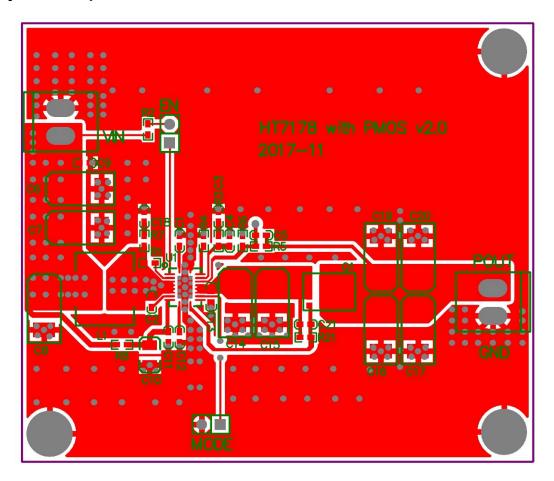

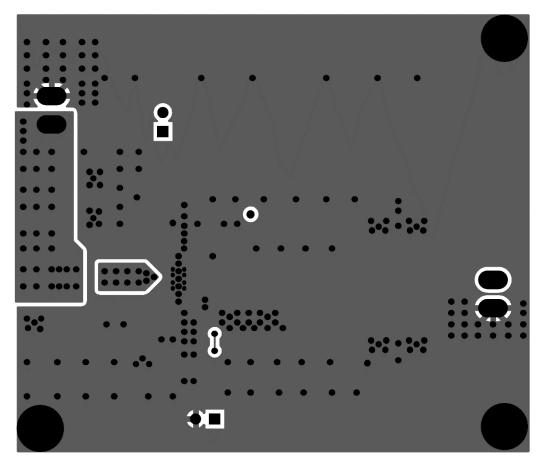

# 3.3. Layout Examples

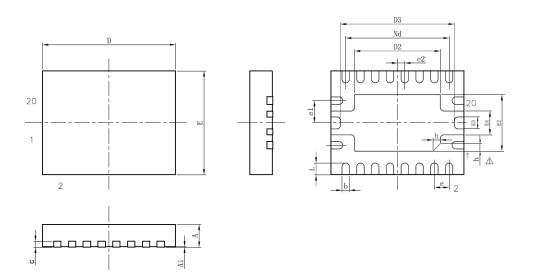

# ■ PACKAGE OUTLINE

| SYMBOL        | MILLIMETER       |          |       |  |  |  |

|---------------|------------------|----------|-------|--|--|--|

| SYMBOL        | MIN              | NOM      | MAX   |  |  |  |

| A             | 0.70             | 0.75     | 0.80  |  |  |  |

| A1            | _                | 0.01     | 0.05  |  |  |  |

| b             | 0.18             | 0.25     | 0.30  |  |  |  |

| c             | 0.18             | 0.20     | 0. 25 |  |  |  |

| D             | 4. 40            | 4. 50    | 4.60  |  |  |  |

| D2            | 3. 10            | 3. 20    | 3. 30 |  |  |  |

| <b>D</b> 3    | 3. 85REF         |          |       |  |  |  |

| e             | 0. 50BSC         |          |       |  |  |  |

| e1            | 0                | . 75BSC  |       |  |  |  |

| e2            | 0                | . 25BSC  |       |  |  |  |

| Nd            | ;                | 3. 50BSC |       |  |  |  |

| Е             | 3. 40            | 3. 50    | 3. 60 |  |  |  |

| E2            | 2. 10            | 2. 20    | 2.30  |  |  |  |

| E3            | 0. 35REF         |          |       |  |  |  |

| E4            | 0. 75REF         |          |       |  |  |  |

| L             | 0.35             | 0.40     | 0.45  |  |  |  |

| h             | 0. 20 0.25 0. 30 |          |       |  |  |  |

| 载体尺寸<br>(mil) | 134*94           |          |       |  |  |  |