# 带LDO模式,过压和过流保护IC 以及锂电池充电器前端保护IC

## 说明

CS5801T 是一个高度集成的电路,旨在保护锂离子电池免受充电电路故障的影响。该IC 可持续监视输入电压、输入电流和电池电压。输入过压保护通过关断内部开关立即停止为充电电路供电。输入保护可将系统电流限制为用户可编程的值,如果过流情况仍存在,则在一个消隐周期之后关断导通元件。此外,该IC 还会监控自身的芯片温度,并在过热时切断电源。该IC 可由一个处理器控制并且可为主机提供关于故障条件的状态信息。

CS5801T提供纤小的DFN2X2\_8L的封装,可以为客户节省可观的PCB面积,其额定的工作温度范围为-40℃至85℃。

## 特性

- · 针对三个变量提供保护:

- -输入过压、快速响应< 1µs

- -带有电流限制的用户可编程过流

- -电池过压

- 30V最大输入电压

- · 支持高达1.5A 的输入电流

- 防止由电流瞬变造成的错误触发

- · 电池防反接保护

- 过热保护

- 輸入使能

- · 状态指示-故障状态

- · 5.15V LDO模式电压调节

### 应用

- · 智能手机

- . MP3播放器

- . 低功耗手持设备

- · 蓝牙耳机等蓝牙设备

## 封装

DFN2X2\_8L

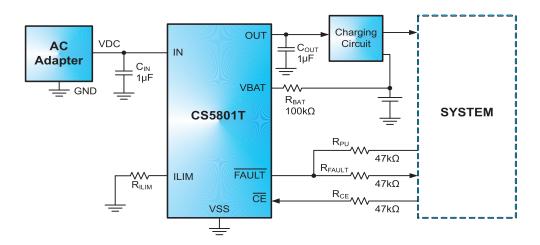

# 典型应用电路

Figure a. 典型应用电路

# OVERVOLTAGE AND OVERCURRENT PROTECTION IC AND Li+ CHARGER FRONT-END PROTECTION IC WITH LDO MODE

### **DESCRIPTION**

The CS5801T is highly integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage, the input current, and the battery voltage. The output acts as a linear regulator. The output is regulated to  $V_{\mbox{\tiny O(REG)}}$  for inputs between  $V_{\mbox{\tiny O(REG)}}$ and the overvoltage threshold. If an input overvoltage condition occurs, the IC immediately removes power from the charging circuit by turning off an internal switch. In the case of an overcurrent condition, it limits the system current at the threshold value, and if the overcurrent persists, switches the pass element OFF after a blanking period. Additionally, the IC also monitors its own die temperature and switches off if it exceeds 140°C. The input overcurrent threshold is user-programmable.

The IC can be controlled by a processor and also provides status information about fault conditions to the host.

# **FEATURES**

- · Provides Protection for Three Variables:

- -Input Overvoltage, with Rapid Response in < 1µs -User-Programmable Overcurrent with Current Limiting

- -Battery Overvoltage

- 30V Maximum Input Voltage

- · Supports up to 1.5A Input Current

- battery anti access protection

- Robust Against False Triggering Due to Current Transients

- · Thermal Shutdown

- Enable Input

- · Status Indication Fault Condition

- 5.1V LDO Mode Voltage Regulation

# Package

DFN2X2\_8L

### **APPLICATIONS**

- · Mobile Phones and Smart Phones PDAs

- MP3 Players

- · Low-Power Handheld Devices

- Bluetooth™ Headsets

### TYPICAL APPLICATION CIRCUIT

Figure a. Typical Application Circuit

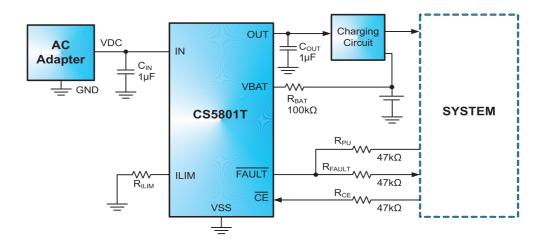

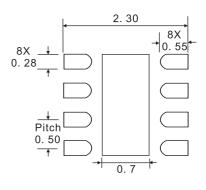

# PIN CONFIGURATION (TOP VIEW)

# **TERMINAL FUNCTIONS**

| TERMINAL    |     |     | DECORPTION                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | PIN | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |  |  |

| IN          | 1   | ı   | nput power. Connect IN to the external DC supply. Bypass IN to VSS with a $1\mu F$ ceramic capacitor minimum).                                                                                                                                                                                                                          |  |  |

| VSS         | 2   | _   | Ground terminal                                                                                                                                                                                                                                                                                                                         |  |  |

| NC          | 3   |     | This pin may have internal circuits used for test purposes. Do not make any external connection to this pin for normal operation.                                                                                                                                                                                                       |  |  |

| FAULT       | 4   | 0   | Open-drain, device status output. FAULT = Low indicates that the input FET Q1 is off due to input overvoltage, input overcurrent, battery overvoltage, or thermal shutdown. FAULT is high impedance during normal operation. Connect a pullup resistor from FAULT to the desired logic level voltage rail.                              |  |  |

| CE          | 5   | I   | Chip enable active low input. Connect $\overline{\text{CE}}$ = High to disable the IC and turn the input FET off. Connect $\overline{\text{CE}}$ = low for normal operation. $\overline{\text{CE}}$ is internally pulled down.                                                                                                          |  |  |

| VBAT        | 6   | ı   | Battery voltage sense input. Connect to the battery pack positive terminal through a resistor.                                                                                                                                                                                                                                          |  |  |

| ILIM        | 7   | I/O | Input overcurrent threshold programming. Connect a resistor from ILIM to VSS to set the overcurrent threshold.                                                                                                                                                                                                                          |  |  |

| OUT         | 8   | 0   | Output terminal to the charging system. Connect OUT to the external load circuitry. Bypass OUT to VSS with a 1µF ceramic capacitor (minimum).                                                                                                                                                                                           |  |  |

| Thermal PAD |     | _   | There is an internal electrical connection between the exposed thermal pad and the VSS pin of the device. The thermal pad must be connected to the same potential as the VSS pin on the printed cir board. Do not use the thermal pad as the primary ground input for the device. The VSS pin must be connected to ground at all times. |  |  |

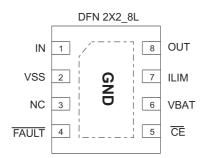

# Simplified Block Diagram(Figure 1)

# **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER            | PIN                                                                    | VALUE                             | UNIT |  |

|------------------|----------------------|------------------------------------------------------------------------|-----------------------------------|------|--|

|                  |                      | IN (with respect to VSS)                                               | -0.3 to 30                        |      |  |

| $V_{I}$          | Input voltage        | OUT (with respect to VSS)                                              | -0.3 to 7                         | V    |  |

|                  |                      | ILIM, FAULT, CE, VBAT (with respect to VSS)                            | -0.3 to 7                         |      |  |

| l <sub>l</sub>   | Input current        | IN                                                                     | 2                                 | Α    |  |

| lo               | Output current       | OUT                                                                    | 2                                 | А    |  |

|                  | Output sink current  | FAULT                                                                  | 15                                | mA   |  |

| ESD              |                      | All (Human Body)                                                       | 2000                              | V    |  |

|                  |                      | All (Machine)                                                          | 200                               | V    |  |

|                  | Withstand Voltage    | All (Charge Device)                                                    | 500                               | V    |  |

|                  |                      | IN (with IN bypassed to the VSS with a 1-μF low-ESR ceramic capacitor) | 15 (Air Discharge)<br>8 (Contact) | kV   |  |

| TJ               | Junction temperature |                                                                        | -40 to 150                        | °C   |  |

| T <sub>stg</sub> | Storage temperature  |                                                                        | -65 to 150                        | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                     |                          | MIN             | MAX | UNIT |

|---------------------|--------------------------|-----------------|-----|------|

| $V_{IN}$            | Input voltage range      | 3.3             | 30  | V    |

| I <sub>IN</sub>     | Input current, IN pin    |                 | 1.5 | Α    |

| I <sub>OUT</sub>    | Output current, OUT pin  |                 | 1.5 | Α    |

| R <sub>(ILIM)</sub> | OCP Programming resistor | 15              | 90  | kΩ   |

| TJ                  | Junction temperature     | <del>-4</del> 0 | 125 | °C   |

# **Order Information**

| Device  | Package   | Making        | Reel Size | Tape Width | Quantity |

|---------|-----------|---------------|-----------|------------|----------|

| CS5801T | DFN2X2_8L | 5801D<br>xxxx | 7"        | 8mm        | 3000     |

**ELECTRICAL CHARACTERISTICS**over junction temperature range –40°C to 125°C and recommended supply voltage (unless otherwise noted)

| •                       | PARAMETER                                      | 125°C and recommended supply voltage ( TEST CONDITIONS                                                                                                        | MIN      | TYP  | MAX   | UNIT      |

|-------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|-----------|

| IN                      | r ANAMETEN                                     | TEST CONDITIONS                                                                                                                                               | IAIIIA   | 115  | IVIAA | CIVIT     |

|                         | Undervoltage lock-out, input power             |                                                                                                                                                               |          |      |       |           |

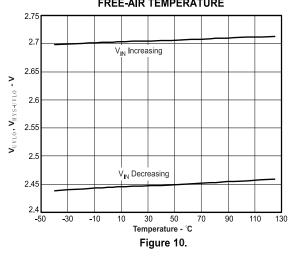

| UVLO                    | detected threshold                             | CE = Low, V <sub>IN</sub> increasing from 0V to 3V                                                                                                            | 2.6      | 2.7  | 2.8   | V         |

| V <sub>hys(UVLO)</sub>  | Hysteresis on UVLO                             | CE = Low, V <sub>IN</sub> decreasing from 3V to 0V                                                                                                            | 160      | 200  | 240   | mV        |

| t <sub>DGL(PGOOD)</sub> | Deglitch time, input power detected status     | $\overline{CE}$ = Low. Time measured from $V_{IN}$ 0V $\rightarrow$ 5V 1 $\mu s$ rise-time, to output turning ON                                              |          | 16   |       | ms        |

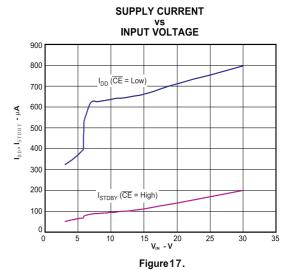

| I <sub>DD</sub>         | Operating current                              | $\overline{\text{CE}}$ = Low, No load on OUT pin,<br>V <sub>IN</sub> = 5V, R <sub>(ILIM)</sub> = 25k $\Omega$                                                 |          | 580  |       | μΑ        |

| I <sub>STDBY</sub>      | Standby current                                | CE = High, V <sub>IN</sub> = 5V                                                                                                                               |          | 75   | 95    | μΑ        |

| INPUT TO C              | OUTPUT CHARACTERISTICS                         |                                                                                                                                                               | 1        |      |       |           |

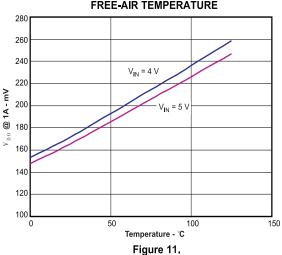

| $V_{DO}$                | Drop-out voltage IN to OUT                     | CE = Low, V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 1A                                                                                                         |          | 250  | 280   | mV        |

| OUPUT VOL               | LTAGE REGULATION                               | 1                                                                                                                                                             | <b>i</b> |      |       |           |

| $V_{O(REG)}$            | Output voltage                                 | $\overline{\text{CE}}$ = Low, V <sub>IN</sub> = 5.7V, I <sub>OUT</sub> = No Load                                                                              | 5        | 5.15 | 5.30  | V         |

| INPUT OVE               | RVOLTAGE PROTECTION                            |                                                                                                                                                               |          |      |       |           |

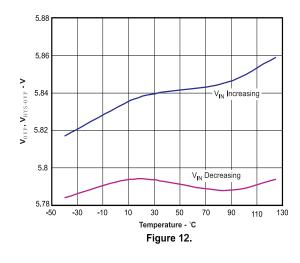

| V <sub>OVP</sub>        | Input overvoltage protection threshold         | CE = Low, V <sub>IN</sub> increasing from 5V to 11V                                                                                                           | 6.65     | 6.8  | 6.95  | ٧         |

| t <sub>PD(OVP)</sub>    | Input OV propagation delay <sup>(1)</sup>      | CE = Low                                                                                                                                                      |          | 200  |       | ns        |

| $V_{hys(OVP)}$          | Hysteresis on OVP                              | CE = Low, V <sub>IN</sub> decreasing from 11V to 5V                                                                                                           | 20       | 100  | 110   | mV        |

| t <sub>ON(OVP)</sub>    | Recovery time from input overvoltage condition | $\overline{\text{CE}}$ = Low, Time measured from $V_{\text{IN}}$ 7.5V $\rightarrow$ 5V, 1 $\mu$ s fall-time                                                   |          | 16   |       | ms        |

| INPUT OVE               | RCURRENT PROTECTION                            |                                                                                                                                                               |          |      |       |           |

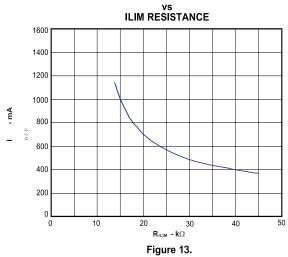

| I <sub>OCP</sub>        | Input overcurrent protection threshold range   |                                                                                                                                                               | 300      |      | 1500  | mA        |

| I <sub>OCP</sub>        | Input overcurrent protection threshold         | $\overline{CE}$ = Low, R <sub>(ILIM)</sub> =15 k $\Omega$ ,<br>3 V ≤ V <sub>IN</sub> < V <sub>OVP</sub> - V <sub>hys(OVP)</sub>                               | 900      | 1000 | 1100  | mA        |

| K <sub>(ILIM)</sub>     | Adjustable current limit factor                |                                                                                                                                                               |          | 15   |       | A =<br>kΩ |

| t <sub>BLANK(OCP)</sub> | Blanking time, input overcurrent detected      |                                                                                                                                                               |          | 240  |       | μs        |

| t <sub>REC(OCP)</sub>   | Recovery time from input overcurrent condition |                                                                                                                                                               |          | 128  |       | ms        |

| BATTERY C               | OVERVOLTAGE PROTECTION                         |                                                                                                                                                               |          |      |       |           |

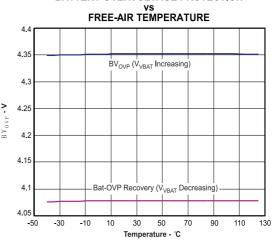

| $BV_{OVP}$              | Battery overvoltage protection threshold       | <u>CE</u> = Low, V <sub>IN</sub> > 4.4V                                                                                                                       | 4.30     | 4.35 | 4.4   | ٧         |

| V <sub>hys(Bovp)</sub>  | Hysteresis on BV <sub>OVP</sub>                | CE = Low, V <sub>IN</sub> > 4.4V                                                                                                                              | 200      | 275  | 320   | mV        |

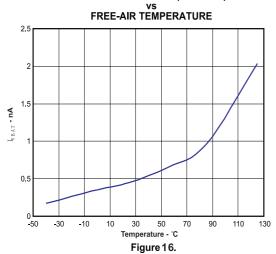

| I <sub>(VBAT)</sub>     | Input bias current on VBAT pin                 | V <sub>(VBAT)</sub> = 4.4V, T <sub>J</sub> = 25°C                                                                                                             |          | -    | 10    | nA        |

| t <sub>DGL(Bovp)</sub>  | Deglitch time, battery overvoltage detected    | $\overline{\text{CE}}$ = Low, V <sub>IN</sub> > 4.4V. Time measured from V <sub>(VBAT)</sub> rising from 4.1V to 4.4V to $\overline{\text{FAULT}}$ going low. |          | 240  |       | μs        |

| THERMAL F               | PROTECTION                                     |                                                                                                                                                               |          |      |       |           |

| $T_{J(OFF)}$            | Thermal shutdown temperature                   |                                                                                                                                                               |          | 140  | 150   | °C        |

| T <sub>J(OFF-HYS)</sub> | Thermal shutdown hysteresis                    |                                                                                                                                                               |          | 20   |       | °C        |

| LOGIC LEV               |                                                |                                                                                                                                                               | I        |      |       |           |

| V <sub>IL</sub>         | Low-level input voltage                        |                                                                                                                                                               | 0        |      | 0.4   | V         |

| V <sub>IH</sub>         | High-level input voltage                       |                                                                                                                                                               | 1.4      |      |       | V         |

| I <sub>IL</sub>         | Low-level input current                        | V <sub>(/CE)</sub> = 0V                                                                                                                                       |          |      | 1     | μΑ        |

| l <sub>IH</sub>         | High-level input current                       | V <sub>(/CE)</sub> = 1.8V                                                                                                                                     |          |      | 15    | μΑ        |

|                         | ELS ON FAULT                                   | T                                                                                                                                                             | 1        |      |       |           |

| V <sub>OL</sub>         | Output low voltage                             | I <sub>SINK</sub> = 5mA                                                                                                                                       |          |      | 0.2   | V         |

| l <sub>lkg</sub>        | Leakage current, FAULT pin HI-Z                | $V_{(/FAULT)} = 5V$                                                                                                                                           |          |      | 10    | μΑ        |

<sup>(1)</sup> Not tested in production. Specified by design.

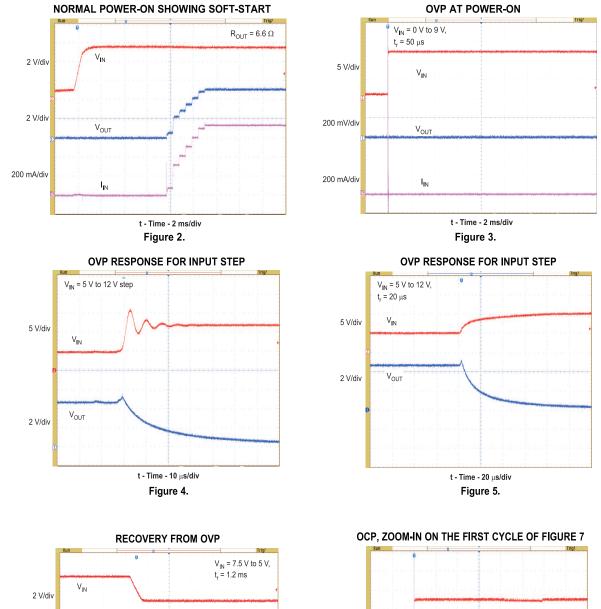

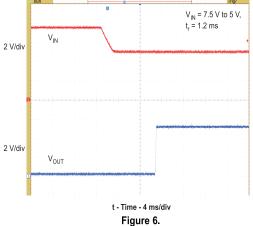

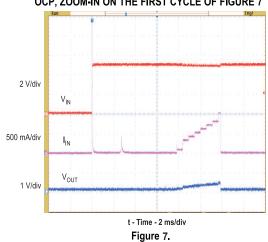

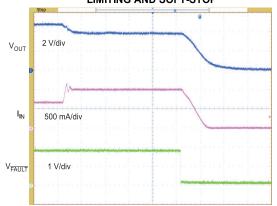

# TYPICAL PERFORMANCE CHARACTERISTICS

Test conditions (unless otherwise noted) for typical operating performance:  $V_{IN}$  = 5 V,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F,  $R_{(ILIM)}$  = 25 k $\Omega$ ,  $R_{BAT}$  = 100 k $\Omega$ ,  $T_A$  = 25°C,  $V_{PU}$  = 3.3V

# **TYPICAL OPERATING PERFORMANCE (continued)**

# $\rm R_{OUT}$ SWITCHES FROM $6.6\Omega$ TO $3.3\Omega, SHOWS$ CURRENT LIMITING AND SOFT-STOP

t - Time - 40  $\mu\text{s}/\text{div}$ Figure 8.

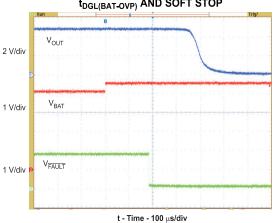

BAT-OVP,  $V_{(VBAT)}$  STEPS FROM 4 V TO 4.5 V,SHOWS  $t_{DGL(BAT-OVP)}$  AND SOFT STOP

Figure 9 .

# **UNDERVOLTAGE LOCKOUT** vs FREE-AIR TEMPERATURE

OVERVOLTAGE THRESHOLD PROTECTION vs FREE-AIR TEMPERATURE

**DROPOUT VOLTAGE (IN to OUT)** vs FREE-AIR TEMPERATURE

INPUT OVERCURRENT PROTECTION

# TYPICAL OPERATING PERFORMANCE (continued)

# INPUT OVERCURRENT PROTECTION VS FREE-AIR TEMPERATURE 985 984 983 982 981 989 979 978 978 977 976 975 -50 -30 -10 10 30 50 70 90 110 130 Temperature - °C Figure 14.

# LEAKAGE CURRENT (VBAT Pin)

# BATTERY OVERVOLTAGE PROTECTION

Figure 15

\_

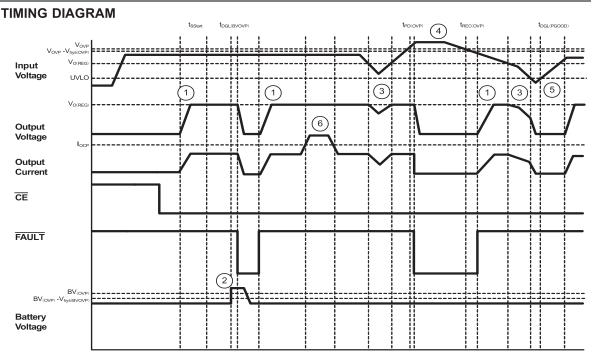

- 1. Normal start-up condition

- 2. Battery over-voltage event

- 3.  $V_{UVLO} < V_{IN} < V_{O(REG)}, V_{OUT}$  tracks  $V_{IN}$

- 4. Input over-voltage event

- 5. Input below UVLO

- 6. High-current event during normal operation

# **DETAILED FUNCTIONAL DESCRIPTION**

CS5801T is a integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage, the input current and the battery voltage. For an input overvoltage condition, the IC immediately removes power from the charging circuit by turning off an internal switch. For an overcurrent condition, it limits the system current at the threshold value, and if the overcurrent persists, switches the pass element OFF after a blanking period. If the battery voltage rises to an unsafe level, the IC disconnects power from the charging circuit until the battery voltage returns to an acceptable value. Additionally, the IC also monitors its own die temperature and switches off if it exceeds 140°C. The input overcurrent threshold is user-programmable. The IC can be controlled by a processor, and also provides status information about fault conditions to the host.

### **POWER DOWN**

The device remains in power down mode when the input voltage at the IN pin is below the undervoltage threshold UVLO. The FET Q1 connected between IN and OUT pins is off, and the status output, FAULT, is set to Hi-Z.

### **POWER-ON RESET**

The device resets when the input voltage at the IN pin exceeds the UVLO threshold. All internal counters and other circuit blocks are reset. The IC then waits for duration  $t_{\tiny \mbox{\scriptsize DGL(PGOOD)}} for the input voltage$ to stabilize. If, after  $t_{\mbox{\tiny DGL(PGOOD)}}\!,$  the input voltage and battery voltage are safe, FET Q1 is turned ON. The IC has a soft-start feature to control the inrush current. The soft-start minimizes the ringing at the input (the ringing occurs because the parasitic inductance of the adapter cable and the input bypass capacitor form a resonant circuit). Because of the deglitch time at power-on, if the input voltage rises rapidly to beyond the OVP threshold, the device will not switch on at all, instead it will go into protection mode and indicate a fault on the FAULT pin.

### **OPERATION**

The device continuously monitors the input voltage, the input current, and the battery voltage as described in detail in the following sections.

### Input Overvoltage Protection

While the input voltage is less than  $V_{\text{\tiny O(REG)}},$  the output voltage tracks the input voltage (less the drop due to the  $R_{\text{\tiny DS(on)}}$  of Q1). When the input voltage is between  $V_{\text{\tiny O(REG)}}$

and  $V_{\text{OVP}}$ , the device functions as a linear regulator and regulates the output voltage to 5.15V. If the input voltage rises above  $V_{\text{OVP}}$ , the internal FET Q1 is turned off, removing power to the output. The response is rapid, with the FET turning off in less than a microsecond. The FAULT pin is driven low. When the input voltage returns below  $V_{\text{OVP}} - V_{\text{hys(OVP)}}$  (but is still above UVLO), the FET Q1 is turned on again after a deglitch time of  $t_{\text{ON(OVP)}}$  to ensure that the input supply has stabilized.

### Input Overcurrent Protection

The overcurrent threshold is programmed by a resistor  $R_{\text{(ILIM)}}$  connected from the ILIM pin to VSS. Figure 13 shows the OCP threshold as a function of  $R_{\text{(ILIM)}}$ , and may be approximated by the following equation:  $I_{\text{OCP}} = 15 \div R_{\text{(ILIM)}}$  (current in A, resistance in  $k\Omega$ )

If the load current tries to exceed the  $I_{\text{OCP}}$  threshold, the device limits the current for a blanking duration of  $t_{\text{BLANK}(\text{OCP})}$ . If the load current returns to less than  $I_{\text{OCP}}$  before  $t_{\text{BLANK}(\text{OCP})}$  times out, the device continues to operate. However,if the overcurrent situation persists for  $t_{\text{BLANK}(\text{OCP})}$ ,  $t_{\text{EE}}$  Q1 is turned off for a duration of  $t_{\text{REC}(\text{OCP})}$ , and the FAULT pin is driven low. The FET is then turned on again after  $t_{\text{REC}(\text{OCP})}$ , and the current is monitored all over again.

To prevent the input voltage from spiking up due to the inductance of the input cable, Q1 is turned off slowly, resulting in a "soft-stop".

### **Battery Overvoltage Protection**

The battery overvoltage threshold BV $_{\text{OVP}}$  is internally set to 4.35V. If the battery voltage exceeds the BV $_{\text{OVP}}$  threshold, the FET Q1 is turned off, and the FAULT pin is driven low. The FET is turned back on once the battery voltage drops to BV $_{\text{OVP}}$  – V $_{\text{hys(Bovp)}}$ . . For a battery overvoltage fault, Q1 is gradually switched OFF.The CS5801T have anti - access protection , if the battery error connected ,the FET Q1 is turned off and the FAULT pin is driven low.

### **Thermal Protection**

If the junction temperature of the device exceeds  $T_{\text{J(OFF)}}$ , the FET Q1 is turned off, and the FAULT pin is driven low. The FET is turned back on when the junction temperature falls below  $T_{\text{J(OFF)}} - T_{\text{J(OFF-HYS)}}$ .

### **Enable Function**

The IC has an enable pin which can be used to enable or disable the device. When the  $\overline{\text{CE}}$  pin is driven high, the internal FET is turned off. When the  $\overline{\text{CE}}$  pin is low, the FET is turned on if other conditions are safe. The  $\overline{\text{CE}}$  pin has an internal pulldown resistor and can be left floating. Note that the  $\overline{\text{FAULT}}$  pin functionality is also disabled when the CE pin is high.

### **Fault Indication**

The FAULT pin is an active-low open-drain output. It is in a high-impedance state when operating conditions are safe, or when the device is disabled by setting  $\overline{CE}$  high. With CE low, the FAULT pin goes low whenever any of these events occurs:

- Input overvoltage

- Input overcurrent

- · IC Overtemperature

- · battery anti access protection

# APPLICATION INFORMATION (WITH REFERENCE TO FIGURE a)

# Selection of R<sub>BAT</sub>

It is strongly recommended that the battery not be tied directly to the VBAT pin of the device, as under some failure modes of the IC, the voltage at the IN pin may appear on the VBAT pin. This voltage can be as high as 30V, and applying 30V to the battery in case of the failure of the CS5801T can be hazardous. Connecting the VBAT pin through  $R_{\rm BAT}$  prevents a large current from flowing into the battery in case of a failure of the IC. In the interests of safety,  $R_{\rm BAT}$  should have a high value. The problem with a large  $R_{\rm BAT}$  is that the voltage drop across this resistor, due to the VBAT bias current  $I_{({\rm VBAT})}$ , causes an error in the BV  $_{\rm OVP}$  threshold. This error is over and above the tolerance on the nominal 4.35V BV  $_{\rm OVP}$  threshold.

Choosing  $R_{\text{BAT}}$  in the range  $100 \text{k}\Omega$  to  $470 \text{k}\Omega$  is a good compromise. In the event of an IC failure, with  $R_{\text{BAT}}$  equal to  $100 \text{k}\Omega$ , the maximum current flowing into the battery would be  $(30 \text{V} - 3 \text{V}) \div 100 \text{k}\Omega = 246 \mu\text{A}$ , which is low enough to be absorbed by the bias currents of the system components.  $R_{\text{BAT}}$  equal to  $100 \text{k}\Omega$  results in a worst-case voltage drop of  $R_{\text{BAT}} \times I_{\text{(VBAT)}} = 1 \text{mV}$ . This is negligible to compared to the internal tolerance of 50 mV on  $BV_{\text{OVe}}$  threshold.

If the Bat-OVP function is not required, the VBAT pin should be connected to VSS.

## Selection of $R_{ce}$ , $R_{fault}$ , and $R_{pu}$

The  $\overline{CE}$  pin can be used to enable and disable the IC. If host control is not required, the  $\overline{CE}$  pin can be tied to ground or left un-connected, permanently enabling the device.

$\overline{\text{CE}}$  pin can be controlled by a host processor. As in the case of the VBAT pin (see above), the  $\overline{\text{CE}}$  pin should be connected to the host GPIO pin through as large a resistor as possible. The limitation on the resistor value is that the minimum  $V_{\text{OH}}$  of the host GPIO pin less the drop across the resistor should be greater than  $V_{\text{IH}}$  of the CS5801T CE pin. The drop across the resistor is given by  $R_{\text{CF}} \times I_{\text{IH}}$ .

The FAULT pin is an open-drain output that goes low during OV, OC, battery-OV, and OT events. If the application does not require monitoring of the FAULT pin, it can be left unconnected. But if the FAULT pin has to be monitored, it should be pulled high externally through  $R_{\text{PU}}$ , and connected to the host through  $R_{\text{FAULT}}$  prevents damage to the host controller if the CS5801T fails (see above). The resistors should be of high value, in practice values between  $22k\Omega$  and  $100k\Omega$  should be sufficient.

# Selection of Input and Output Bypass Capacitors

The input capacitor  $C_{IN}$  in Figure a is for decoupling, and serves an important purpose. Whenever there is a step change downwards in the system load current, the inductance of the input cable causes the input voltage to spike up. C<sub>IN</sub> prevents the input voltage from overshooting to dangerous levels. It is recommended that a ceramic capacitor of at least 1µF be used at the input of the device. It should be located in close proximity to the IN  $pin.C_{out}$  in Figure a is also important: If a fast (< 1µ s rise time) overvoltage transient occurs at the input, the current that charges C<sub>OUT</sub> causes the device's current-limiting loop to start, reducing the gate-drive to FET Q1. This results in improved performance for input overvoltage protection.  $C_{\text{out}}$  should also be a ceramic capacitor of at least  $1\mu F$ , located close to the OUT pin.  $C_{\text{out}}$  also serves as the input decoupling capacitor for the charging circuit downstream of the protection IC.

# **Powering Accessories**

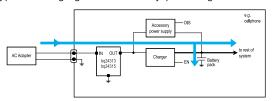

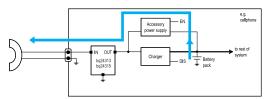

In some applications, the equipment that the protection IC resides in may be required to provide power to an accessory (e.g. a cellphone may power a headset or an external memory card) through the same connector pins that are used by the adapter for charging. Figure 18 and Figure 19 illustrate typical charging and accessory-powering scenarios:

Figure 18 . Charging - The Red Arrows Show the Direction of Current Flow

Figure 19 . Powering an Accessory - The Red Arrows Show the Direction of Current Flow

In the second case, when power is being delivered to an accessory, the CS5801T device is required to support current flow from the OUT pin to the IN pin. If  $V_{\text{OUT}} > \text{UVLO} + 0.7\text{V}$ , FET Q1 is turned on, and the reverse current does not flow through the diode but through Q1. Q1 remains ON as long as  $V_{\text{OUT}} > \text{UVLO} - V_{\text{hys(UVLO)}} + R_{\text{DS(on)}} \times I_{\text{(ACCESSORY)}}$ . Within this voltage range, the reverse current capability is the same as the forward capability, 1.5A. It should be noted that there is no overcurrent protection in this direction.

## **PCB Layout Guidelines:**

This device is a protection device, and is meant to protect down-stream circuitry from hazardous voltages. Potentially, high voltages may be applied to this IC. It has to be ensured that the edge-to-edge clearances of PCB traces satisfy the design rules for high voltages.

The device uses DFN2X2\_8L packages with a PowerPAD™. For good thermal performance, the PowerPAD should be thermally coupled with the PCB ground plane. In most applications, this will require a copper pad directly under the IC. This copper pad should be connected to the ground plane with an array of thermal vias.

$C_{\text{IN}}$  and  $C_{\text{OUT}}$  should be located close to the IC. Other components like  $R_{\text{(ILIM)}}$  and  $R_{\text{BAT}}$  should also be located close to the IC.

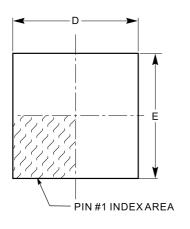

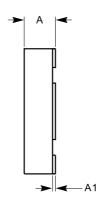

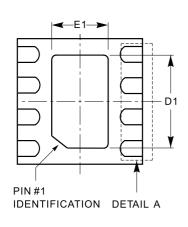

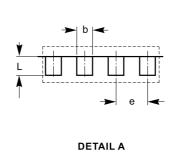

# PACKAGE OUTLINE DIMENSIONS

CS5801T DFN 2X2\_8L

| SYMBOL | MIN            | NOM     | MAX  |  |  |

|--------|----------------|---------|------|--|--|

| Α      | 0.70           | 0.75    | 0.80 |  |  |

| A1     | 0.00           | 0.02    | 0.05 |  |  |

| b      | 0.18           | 0.25    | 0.30 |  |  |

| D      | 2.00BSC        |         |      |  |  |

| D1     | 1.10 1.20 1.30 |         |      |  |  |

| E      |                | 2.00BSC |      |  |  |

| E1     | 0.50           | 0.60    | 0.70 |  |  |

| е      | 0.50 BSC       |         |      |  |  |

| L      | 0.30           | 0.35    | 0.40 |  |  |

**TOP VIEW**

SIDE VIEW

UNIT:mm

# **BOTTOM VIEW**