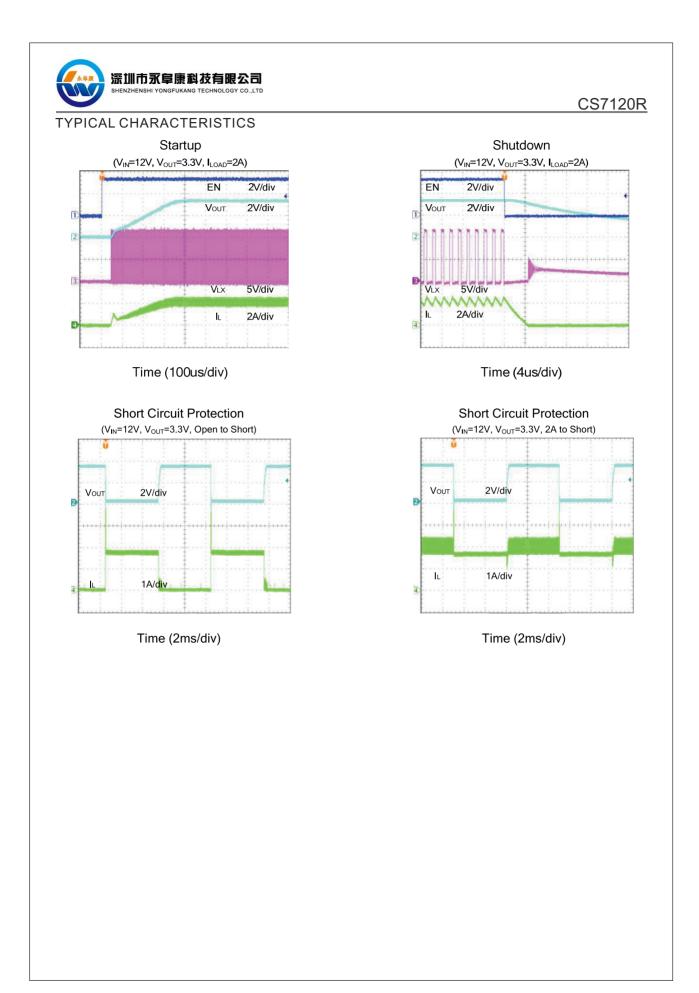

#### **深圳市永阜康科技有限公司** ENZHENSHI YONGFUKANG TECHNOLOGY CO., LTD

CS7120R

# High Efficiency Fast Response, 2A, 22V Input Synchronous Step Down Regulator

## **General Description**

CS7120R develops high efficiency synchronous stepdown DC-DC converter capable of delivering 2A load current . CS7120R operates over a wide input voltage range from 4.5V to 22V and integrates main switch and synchronous switch with very low RDS(0N) to minimize the conduction loss.

CS7120R adopts the instant PWM architecture to achieve fast transient responses for high step down applications and high efficiency at light loads. In addition, it operates under heavy load conditions to minimize the size of inductor and capacitor.

## Features

- Low RDS(ON) for internal switches (top/bottom): 145/135 mΩ

- 4.5-22V input voltage range .

- 2A load current capability .

- •

Instant PWM architecture to achieve fast transient responses Internal softstart limits the inrush current

- 2% 0.6V reference

- RoHS Compliant and Halogen Free •

- Compact package: SOT23-6 •

- Applications

- Set Top Box

- Portable TV

- Access Point Router

- DSL Modem

- LCD TV

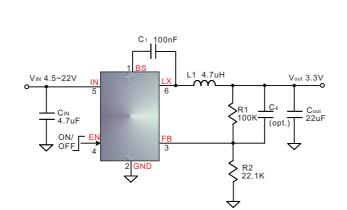

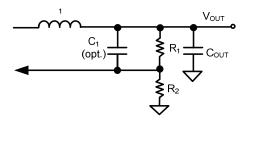

Figure1.Schematic Diagram

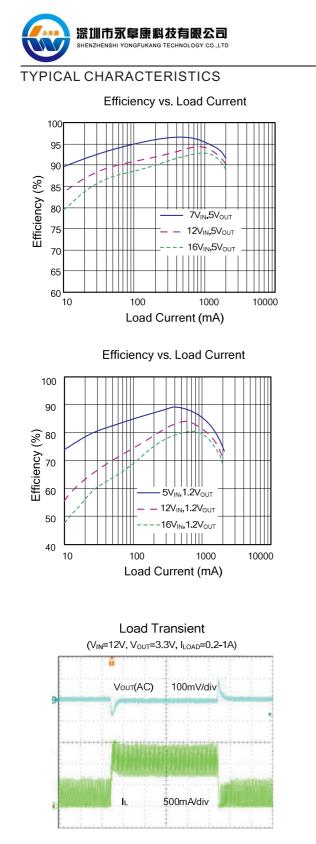

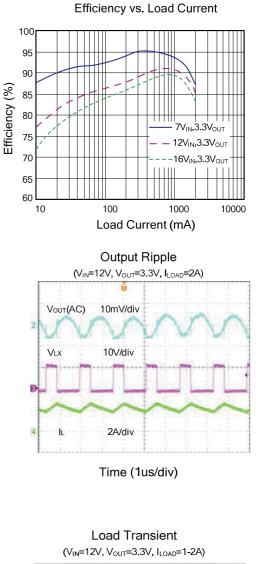

Efficiency VS.Load Current 100 90 Efficiency(%) 80 70 12 ,3.3Vou 60 50 0.5 1 15 2 0 Load Current(A)

## Figure2.Efficiency Figure

#### TEL:0755-82863877 13242913995 E-MAIL:panxia168@126.com http://www.szczkjgs.com

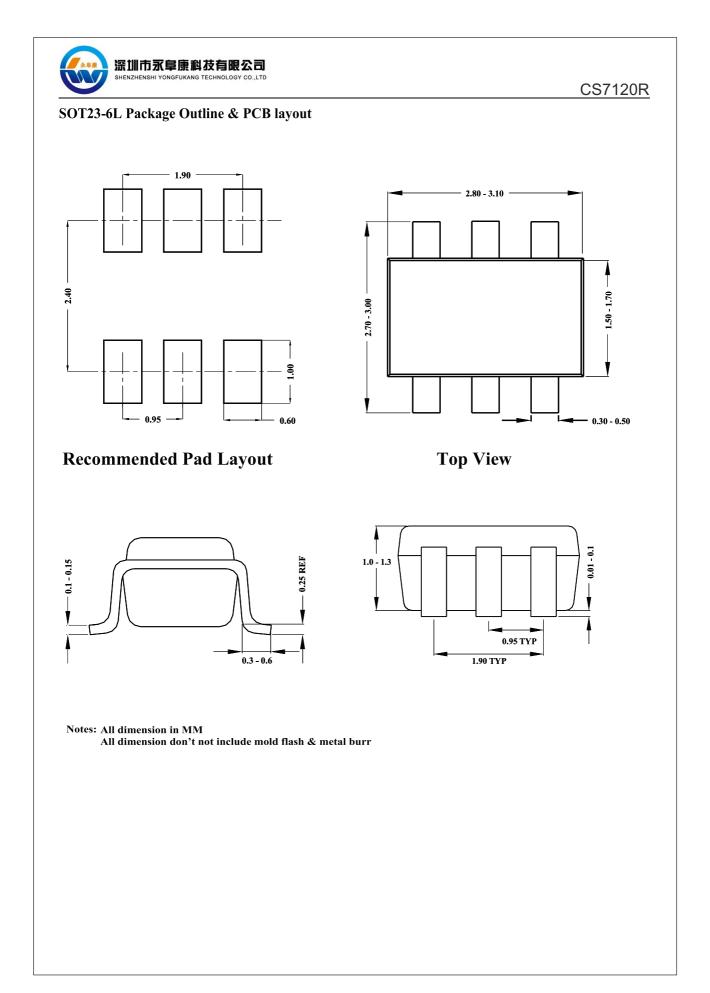

## Package

SOT23-6

**Typical Applications**

CS7120R

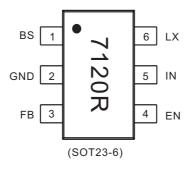

# PIN Configuration and Functions

| NO | NAME | I/O | DESCRIPTION                                                                                                                                                       |

|----|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

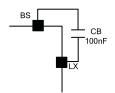

| 1  | BS   | I   | Boot-Strap Pin. Supply high side gate driver. Decouple this pin to LX pin with 0.1 uF ceramic cap.                                                                |

| 2  | GND  | Р   | Ground pin                                                                                                                                                        |

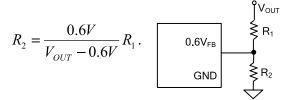

| 3  | FB   | I   | Output Feedback Pin. Connect this pin to the center point of the output resistor divider (as shown in Figure 1) to program the output voltage: Vout=0.6*(I+RI/R2) |

| 4  | EN   | Ι   | Enable control. Pull high to turn on. Do not float.                                                                                                               |

| 5  | IN   | I   | Input pin. Decouple this pin to GND pin with at least luF ceramic cap                                                                                             |

| 6  | LX   | Ο   | Inductor pin. Connect this pin to the switching node of inductor                                                                                                  |

# Absolute Maximum Ratings (Note 1)

| Supply Input Voltage                   | -23V       |

|----------------------------------------|------------|

| LX, EN Voltage                         | -IN + 0.3V |

| FB, BS-LX Voltage                      | - 4V       |

| Power Dissipation, PD@ TA= 25°CSOT23-6 | -0.6W      |

# Package Thermal Resistance (Note 2)

| $\theta_{JA}$                                                       | -170°C/W       |

|---------------------------------------------------------------------|----------------|

| θ <sub>JC</sub>                                                     | -130°C/W       |

| Junction Temperature Range<br>Lead Temperature (Soldering, 10 sec.) |                |

| Storage Temperature Range                                           | -65°C to 150°C |

## Package Thermal Resistance (Note 3)

| Supply Input Voltage       | 4.5V to 22V                       |

|----------------------------|-----------------------------------|

| Junction Temperature Range |                                   |

| Ambient Temperature Range  | <ul> <li>-40°C to 85°C</li> </ul> |

# Order Information

| Device  | Device Package |  | Making Reel Size |     | Quantity |  |

|---------|----------------|--|------------------|-----|----------|--|

| CS7120R | SOT23L-6       |  | 7"               | 8mm | 3000     |  |

# CS7120R

### **Electrical Characteristics**

(VIN=12V, VOUT = 1.2V, L = 25uH, COUT = I0uF, T<sub>A</sub>=25°C, IOUT = 1A utaless otherwise specified)

| Parameter                          | Symbol                  | Test Conditions                         | Min   | Тур   | Max   | Unit |

|------------------------------------|-------------------------|-----------------------------------------|-------|-------|-------|------|

| Input Voltage Range                | V <sub>IN</sub>         |                                         | 4.5   |       | 22    | V    |

| Quiescent Current                  | IQ                      | $I_{OUT}=0, V_{FB}=V_{REF}\times 105\%$ |       | 0.1   |       | μA   |

| Shutdown Current                   | I <sub>SHDN</sub>       | EN=0                                    |       | 5     | 10    | μA   |

| Feedback Reference<br>Voltage      | V <sub>REF</sub>        |                                         | 0.588 | 0.6   | 0.612 | V    |

| FB Input Current                   | I <sub>FB</sub>         | V <sub>FB</sub> =V <sub>IN</sub>        | -50   |       | 50    | nA   |

| Top FET RON                        | R <sub>DS(ON)1</sub>    |                                         |       | 0.145 |       | Ω    |

| Bottom FET RON                     | R <sub>DS(ON)2</sub>    |                                         |       | 0.135 |       | Ω    |

| TOP FET Peak Current<br>Limit      | I <sub>LIM,TOP</sub>    |                                         |       |       | 3.6   | А    |

| Bottom FET Valley<br>Current Limit | I <sub>LIM,BOTTOM</sub> |                                         | 2     |       |       | А    |

| EN Rising Threshold                | V <sub>ENH</sub>        |                                         | 1.5   |       |       | V    |

| EN Falling Threshold               | V <sub>ENL</sub>        |                                         |       |       | 0.4   | V    |

| Input UVLO Threshold               | V <sub>UVLO</sub>       |                                         |       |       | 4.5   | V    |

| Switching Frequency                | F <sub>SW</sub>         |                                         |       | 500   |       | kHz  |

| Min ON Time                        |                         |                                         |       | 50    |       | ns   |

| Min Off Time                       |                         |                                         |       | 100   |       | ns   |

| Soft-start Time                    | t <sub>SS</sub>         |                                         |       | 800   |       | us   |

| Thermal Shutdown<br>Temperature    | T <sub>SD</sub>         |                                         |       | 150   |       | °C   |

| Thermal Shutdown<br>Hysteresis     | T <sub>HYS</sub>        |                                         |       | 15    |       | °C   |

Note 1: Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those mdicated in the operational sections of the specifications is not implied Exposure to absolule maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2:  $0_{JA}$  is measured in tile natural convection at TA =  $25^{\circ}C$  on a low effective single layer tilermal conductivity test board of JEDEC 51-3 thermal measurement standard. Pin 2 of SOT-23-6 packages is the case position for  $0_{JC}$  measurement

Note 3: The device is not guaranteed to function outside its operating conditions.

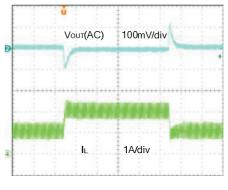

Time 40us/div

# CS7120R

Time 40us/div

#### Operation

CS7120R is a synchronous buck regulator ic that integrates the PWM control, top and bottom switches on the same die to minimize the switching transition loss and conduction loss. With ultra low Rds(on) power switches and proprietary PWM control, this regulator IC can achieve the highest efficiency aad the highest switch frequency simultaneously to minimize the external inductor and capacitor size, and thus achieving the minimytm solutioa footprint CS7120R provides piotection fimctions such as cycle by cycle current limiting and thermal shutdown piotection. CS7120R will sense the output voltage conditions for the feult protection.

#### Applications Information

Because of the high mtegration in the CS7120R IC, the application circuit based on this regulator IC is rather simple. Only input capacitor Cin output capacitor Cout, output inductor L and feedback resistors (R1 and R2) need to be selected for the targeted applications specifications.

#### Feedback resistor dividers Ri and R2:

Choose R1 and R2 to program the proper output voltage. To minimize the power consumption under light loads, it is desirable to choose large resistance values for both R1 and R2. A value of between  $10k\Omega$  and  $1M\Omega$  is highly recommended for both resistors. If Vout is 3.3V, R1=100k is chosen, then using following equation, R2 can be calculated to be 22.1k:

Input capacitor CIN :

The ripple current through input capacitor is calculated as :

$$\mathbf{I}_{\text{CIN}_{\text{RMS}}} = \mathbf{I}_{\text{OUT}} \cdot \sqrt{\mathbf{D}(1-\mathbf{D})} \cdot$$

To minimize the potential noise problem, place a typical X5R or better grade ceramic capacitor really close to the IN and GND pins. Care shouMbe taken to minimize the loop area formed by C<sub>IN</sub>,and IN/GND pins.In this case,a 4.7uF low ESR ceramic capacitor is recommended.

#### Output capacitor Cout:

The output capacitor is selected to handle the output ripple noise requirements. Both steady state ripple and transient requirements must be taken into consideration when selecting this capacitor. For the best performance, it is recommended to use X5R or better grade ceramic capacitor greater than 22uF capacitance.

#### Output inductor L:

There are several considerations in choosing this inductor.(1) Choose the inductance to provide the desired ripple current. It is suggested to choose the ripple current to be about 40% of the maximum output current. The inductance is calculated as:

$$L = \frac{V_{OUT}(1 - V_{OUT}/V_{IN,MAX})}{F_{SW} \times I_{OUT MAX} \times 40\%}$$

where Fsw is the switching frequency and lout,MAX is the maximum load current.The CS7120R regulator IC is quite tolerant of different ripple current amplitude. Consequently, the final choice of inductance can be slightly the calculation value without sigtificanfly impacting the performance.(2) The saturation current rating of the inductor must be selected to be greater than the peak inductor current under fiill load conditions.

Isat, MIN > IOUT, MAX +

$$\frac{\text{VOUT}(1-\text{VOUT}/\text{VIN},\text{MAX})}{2 \cdot \text{Fsw} \cdot \text{L}}$$

(3) The DCR of the inductor and the core loss at the switching frequency must be low enough to achieve the desired efficiency requirement. It is desirable to choose an inductor with DCR<50m $\Omega$  to achieve a good overall efficiency.

#### External Boostrao Cap

This capacitor provides the gate driver voltage for internal high side MOSEFET. A 100nF low BSR ceramic capacitor connected between BS pin and LX pin is recommended.

#### Load Transient Considerations::

The CS7120R regulator IC integrates the compensation components to achieve good stability and fast transient responses. In some applications, adding a 22pF ceramic cap in parallel with R1 may further speed up the load transient responses and is thus recommended for applications with large load transient step requirements.

深圳市永阜康科技有限公司

# CS7120R

## Layout Design:

The layout design of CS7120R regulator is relatively simple. For the best efficiency and minimum noise procablem, we should place the following components close to the IC: CIN, L, R1 and R2.

1) It is desirable to maximize the PCB copper area connecting to GND pin to achieve the best thermal and noise performance. If the board space allowed, a ground plane is highly desirable.

2)  $C_{\text{IN}}$  must be close to Pins IN and GND. The loop) area fomedby Croand GND must be minmized.

3) The PCB copper area associated with LX pin must be minimized to avoid the potential noise problem.

4) The components R1 and R2, and the trace connecting to the FB pin must NOT be adjacent to the LX net on the PCB layout to avoid the noise problem.

5) If the system chip interfecing with the EN pin has a high impedance state at shutdown mode and the IN pin is connected directly to a power source such as a Li-Ion battery, it is desirable to add a pull down 1Mohm resistor between the EN and GND pins to prevent the noise from falsely turning on the regulator at shutdown mode.

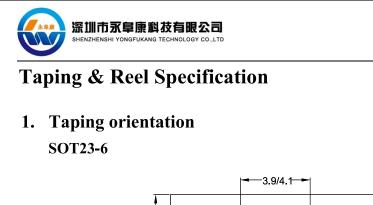

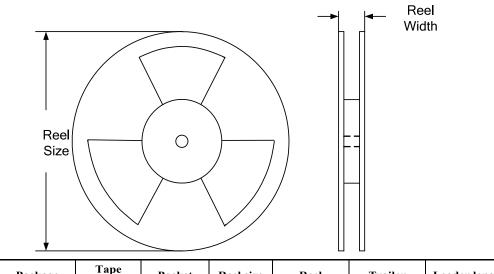

2. Carrier Tape & Reel specification for packages

| Package<br>types | Tape<br>width<br>(mm) | Pocket<br>pitch(mm) | Reel size<br>(Inch) | Reel<br>width(mm) | Trailer<br>length(mm) | Leader length<br>(mm) | Qty per<br>reel |

|------------------|-----------------------|---------------------|---------------------|-------------------|-----------------------|-----------------------|-----------------|

| SOT23-6          | 8                     | 4                   | 7"                  | 8.4               | 280                   | 160                   | 3000            |